Attiny13 Software Uart Bascom

• This video and mp3 song of Zindagi rahi to tujhe taare bhi dila du yaar tera berozgar hai dj sagar kanker ut mix is published by All Cg UT Track All Famous Dj on 11 May 2018. Zindagani banaya hai tujhe mp3 dntrc download. • This video and mp3 song of Zindagi rahi ta tainu bangle bana du is published by Joshi Shivam on 14 Nov 2018.

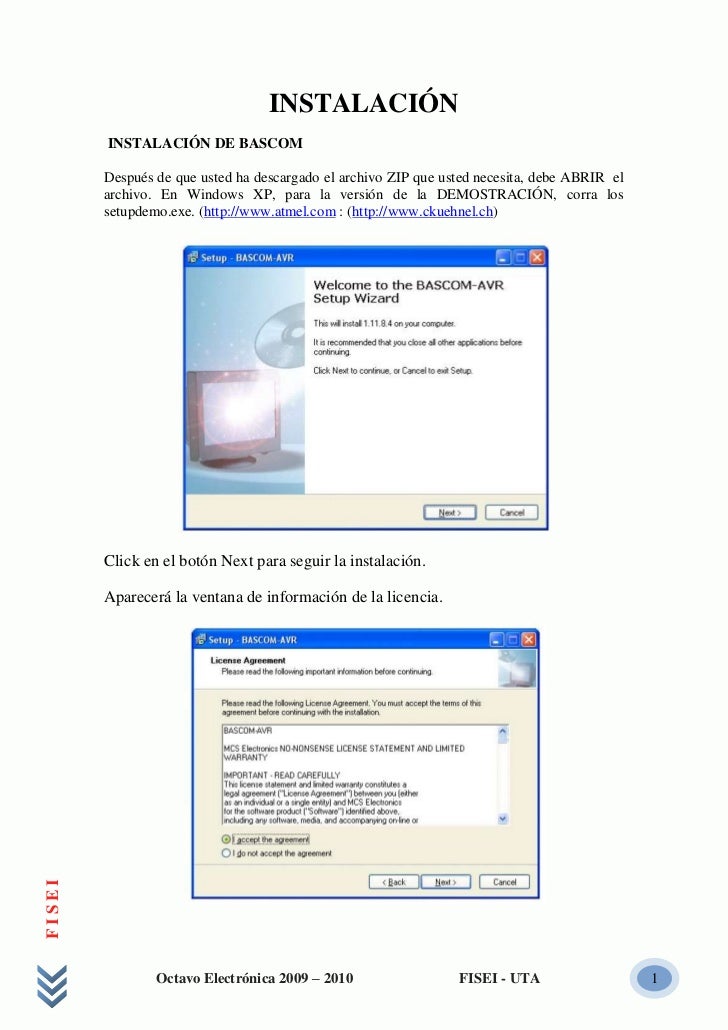

Course on BASCOM AVR - (31) Theoretic/Practical course on BASCOM AVR Programming. Author: DAMINO Salvatore. SOFTWARE UART MANAGEMENT Sometimes it happens that an application requires more serial lines than those available on the selected microcontroller. What can be done to solve this problem, in an easy and efficient mode? Software UART The AT90S2313 and most other AVR controllers has a hardware UART on pins 2 and 3. Sometimes you have to use these pins for another purpose. Bascom has a software UART function that uses extra program space, but you may specify which pins to use for RxD and TxD. The pins to use are specified in the Open command.

I did not find much information about how can you calculate the time using timer1 on Atiny 85. All tutorials are dealing with timer0, Timer 1 is a particular one is not compatible with others, It has precallers from 1/2-1/16384 Synchronous Clocking Mode. The problem is that about any prescaler I chose lets say on internal clock 8Mhz with normal formula. (1/clock)*prescaler=Timer tick.I get totally different timing than one expected.I load the time on OCR1A and toggle some pins the time is much less. I cleared before TCCR1=0 so does not have other prescaler set.

Can you give me a hint on what is going on?I did not find any info on how to calculate timing on timer 1.It seems different than normal timer0 I can manually trial and error tweak for the value I need but this is not professional. If you want accurate timing, say for sampling a serial UART input, then you are much better off using the hardware to reset the counter as there will be no lag. If you reset the counter inside your interrupt service routine then you are going to have to account for the drift introduced by running the code. The ISR preamble takes about 42 CPU cycles to execute; there is overhead to execute the interrupt, disable global interrupts and to save registers. So in your example the counter reset is apx 43 CPU cycles after the compare match. So after the initial two toggles, the pin is being toggled every 93 (50 + 43) CPU clock cycles. Code lag on executing a timed action can be fine, e.g.

Toggling the pin 45 CPU cycles after a compare match that triggers an interrupt every 100 cycles would still give you a pin that toggled every 100 cycles. However introducing code lag into the reset of your counter changes the actual timing.